index

- fetch e aggiornamento PC

- operazioni ALU e accesso memoria

- [[#operazioni ALU e accesso memoria#esercizi|esercizi]]

- salti condizionati (beq)

- con control unit

- segnali di controllo

- tempi di esecuzione

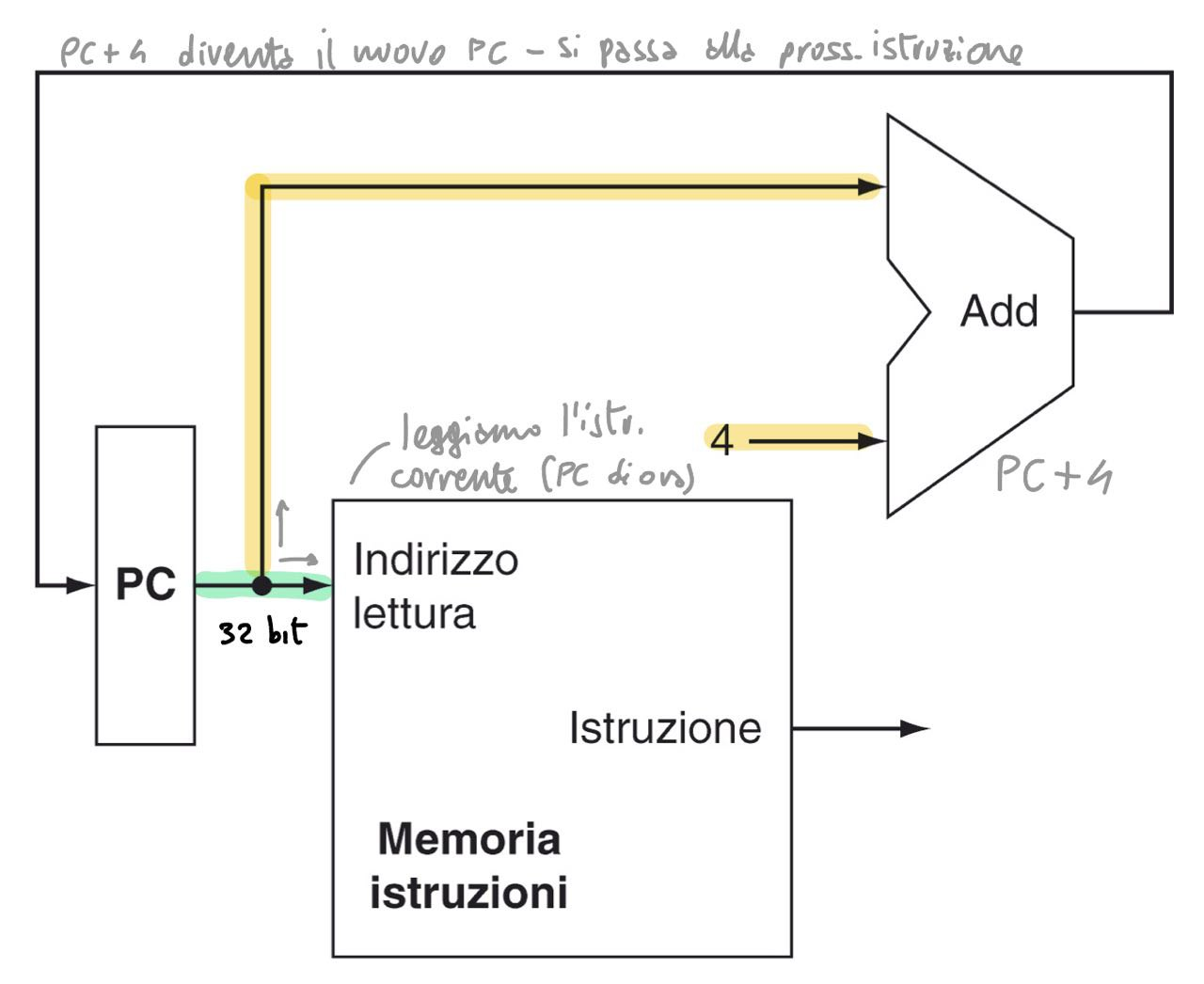

fetch e aggiornamento PC

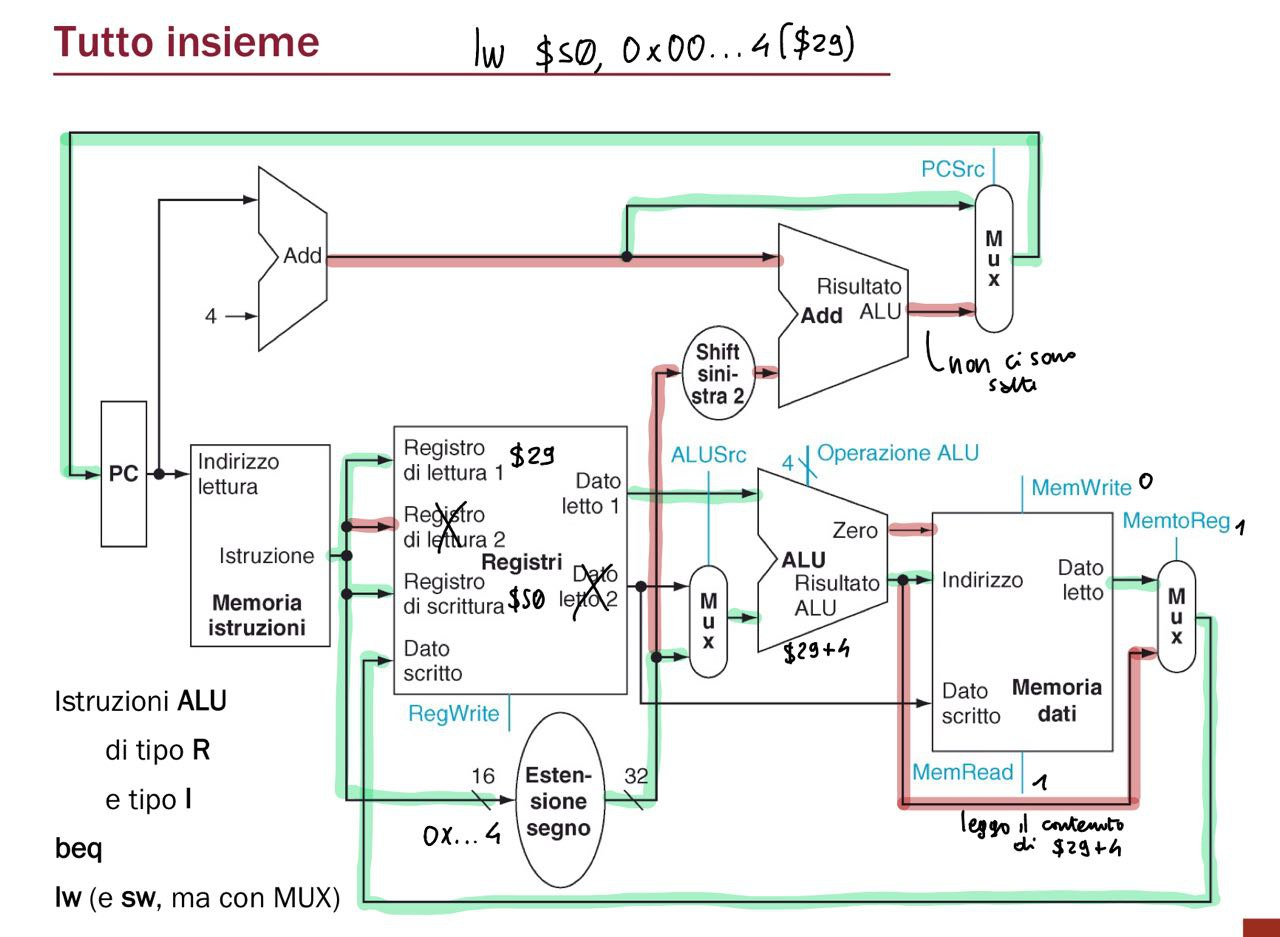

leggiamo l’istruzione corrente e, in parallelo, aggiorniamo il PC

operazioni ALU e accesso memoria

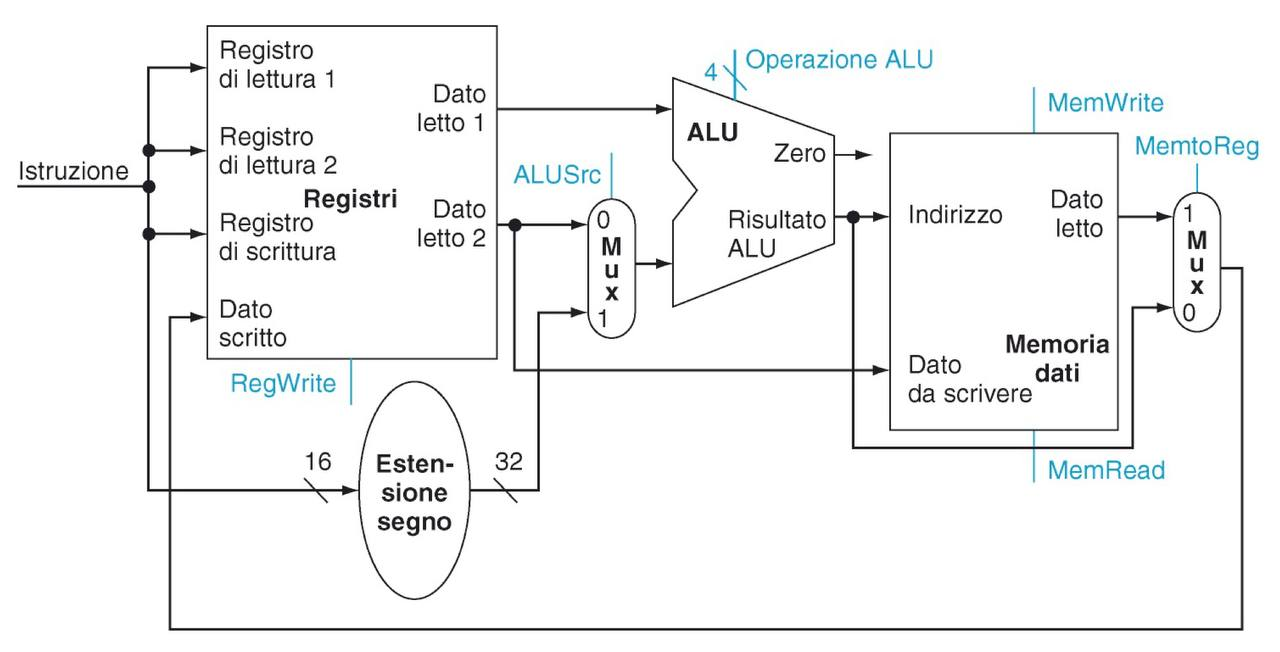

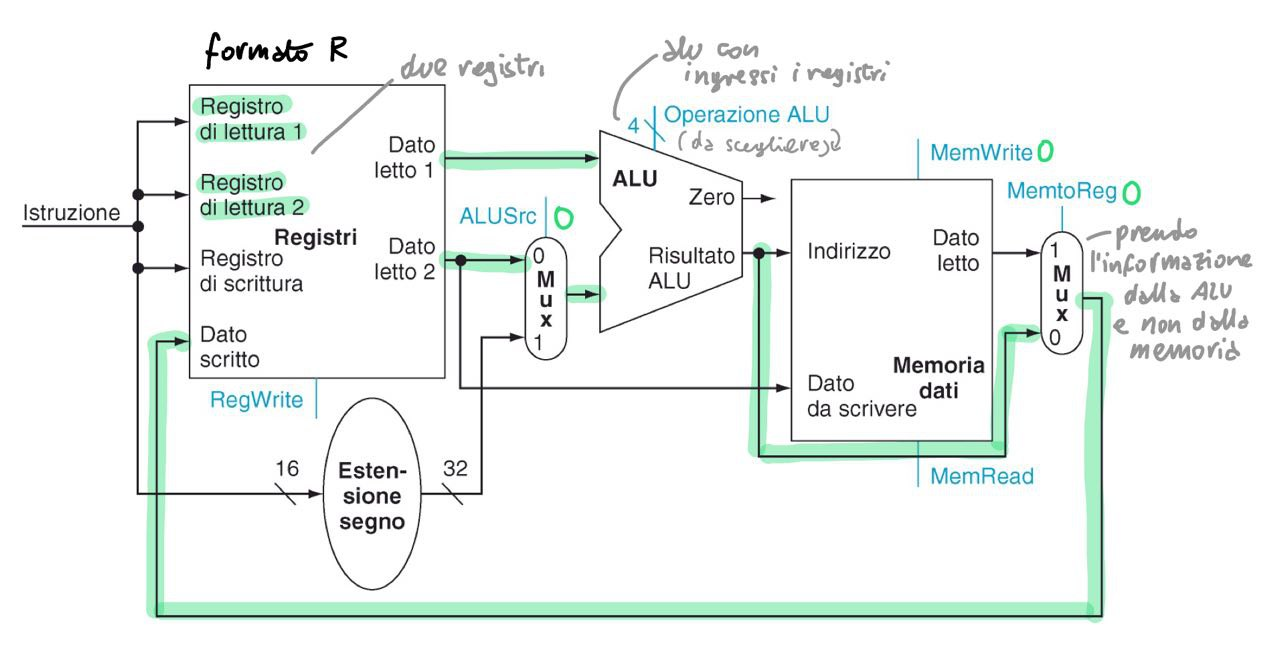

I formati delle istruzioni I (immediato, come load e store word) ed R (aritmetico-logiche) sono quasi uguali: (vedi formati)

- il secondo argomento dell’istruzione è:

- registro - formato R

- campo immediato (ovvero valore esteso nel segno) - formato I

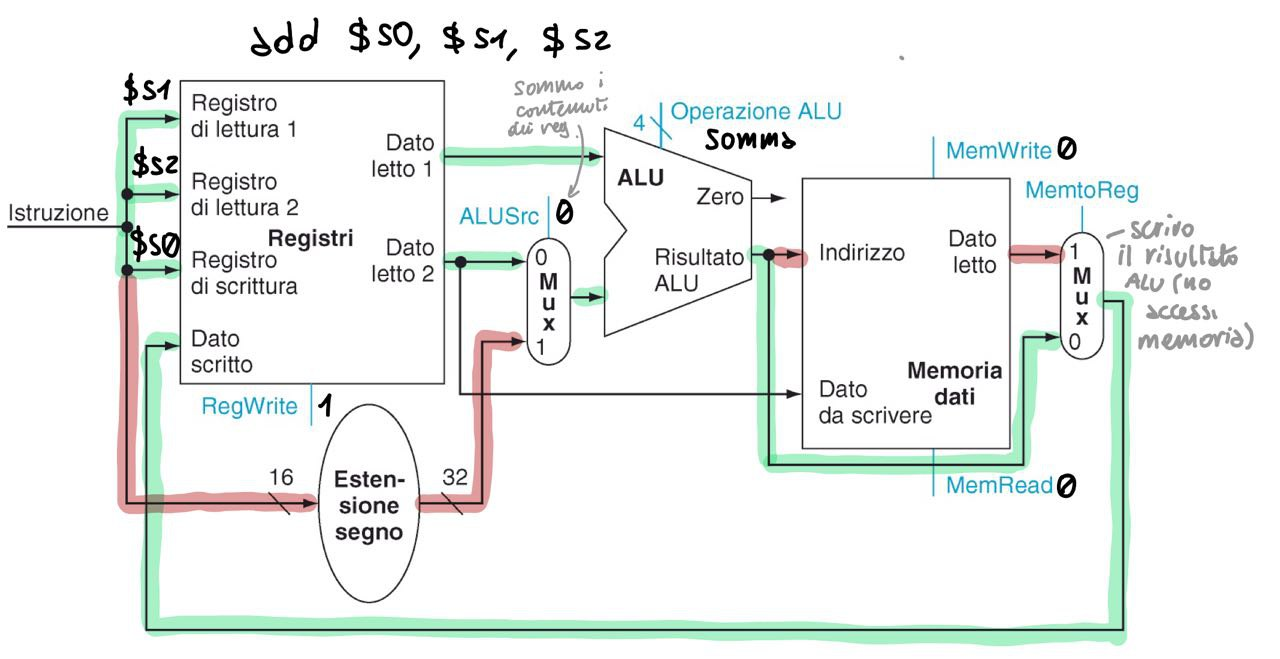

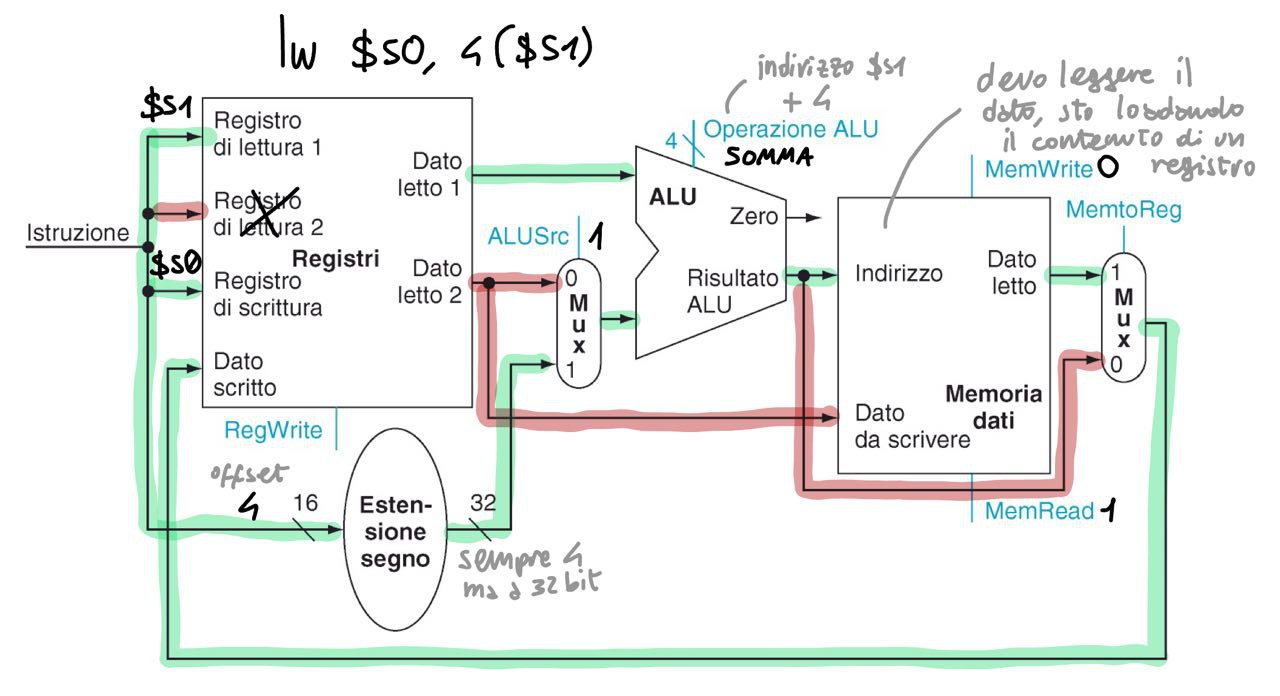

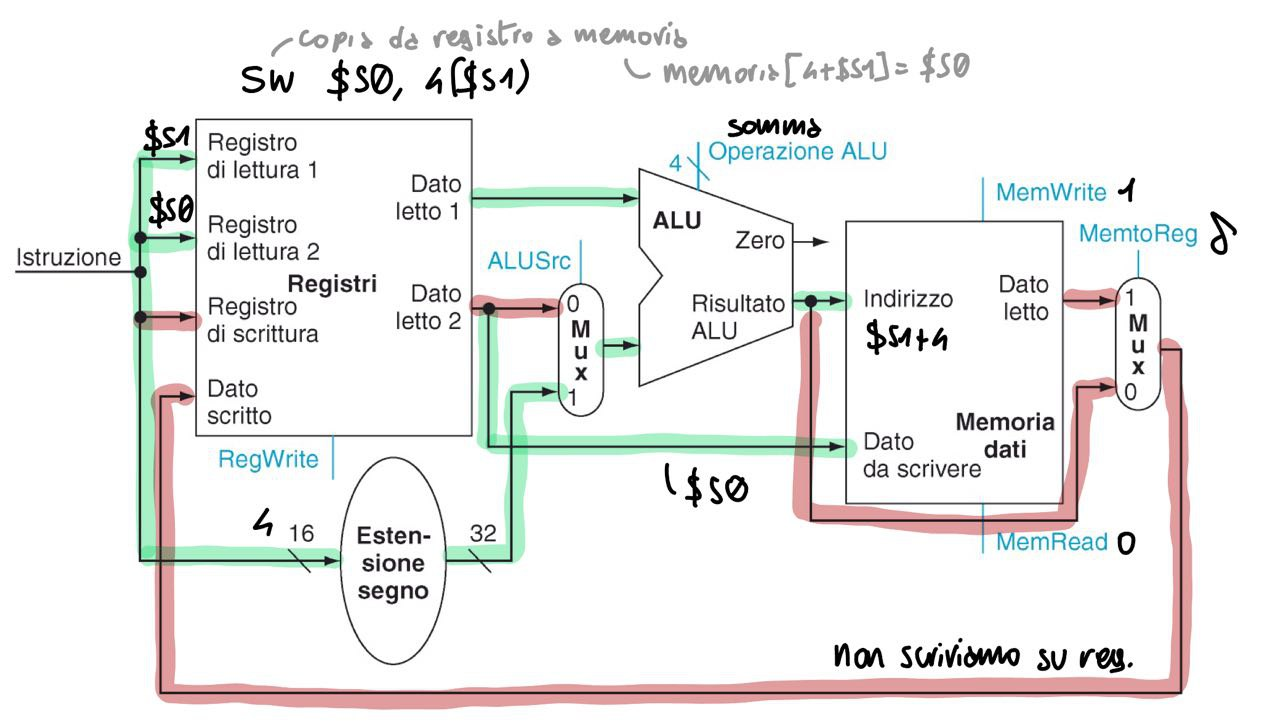

Primo MUX: Le istruzioni aritmetico-logiche utilizzano la ALU con due registri come ingressi, mentre quelle di memoria utilizzano la ALU per calcolare l’indirizzo della memoria dati, ma prendono il secondo ingresso della ALU dal campo offset a 16 bit (con estensione del segno). Quindi il MUX con segnale di controllo ALUSrc sceglie tra queste due opzioni.

Secondo MUX: Il valore da scrivere nel registro di destinazione proviene dalla ALU per le istruzioni di tipo R o dalla memoria per l’istruzione load. Quindi il MUX a destra, con segnale di controllo MemtoReg, sceglie tra le due opzioni.

esempio - istruzioni formato R

esercizi

add

load word

store word

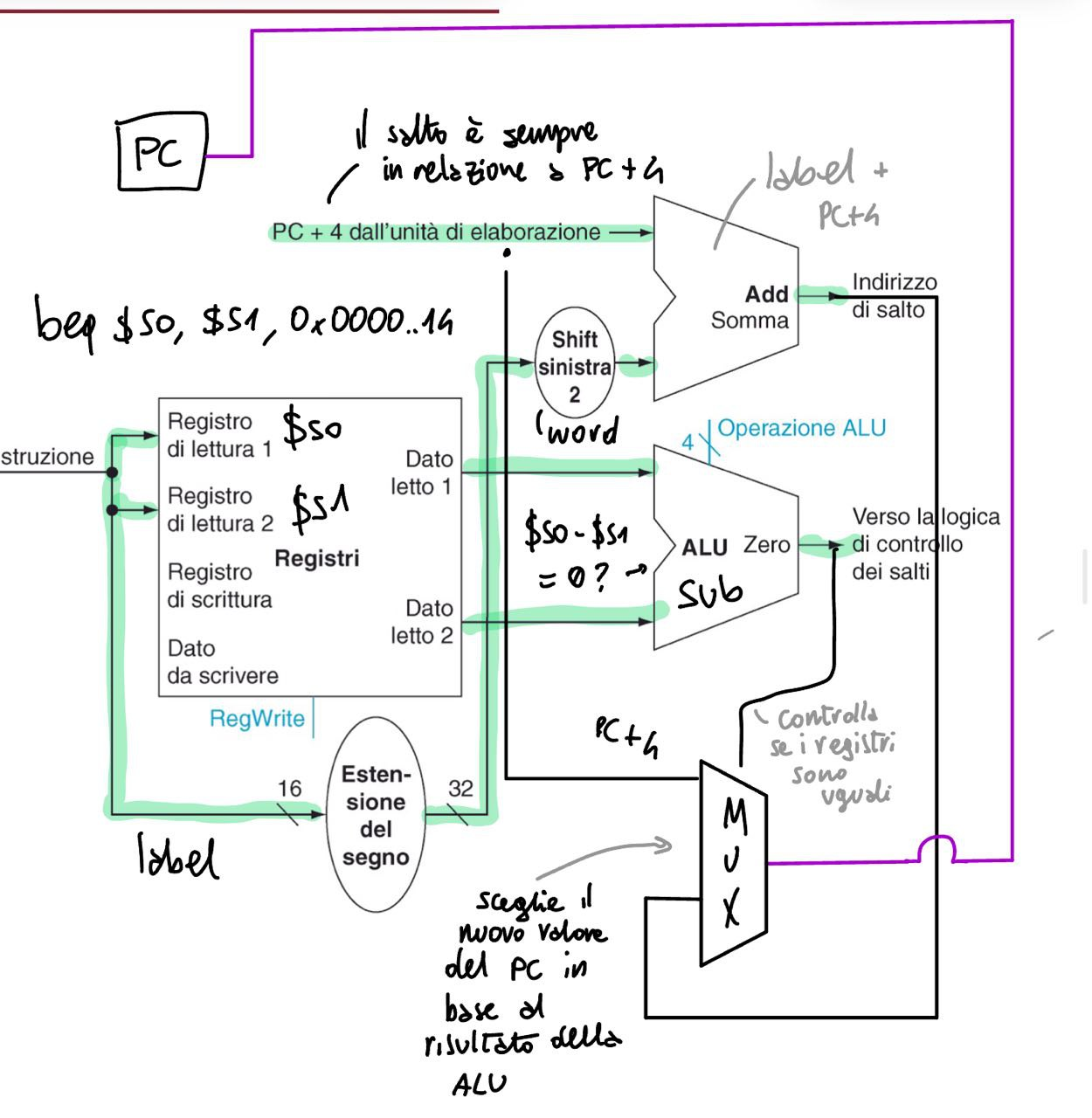

salti condizionati (beq)

-

beqha come operandi: due registri da comparare, un indirizzo a cui saltare (da sommare al PC) -

visto che l’istruzione calcola già l’istruzione successiva al salto, si usa già PC+4 come base per il calcolo

-

anche il campo offset è spostato di 2 bit a sinistra (moltiplicato per 4), perché ci spostiamo di word e non byte.

load word con tutto

con control unit

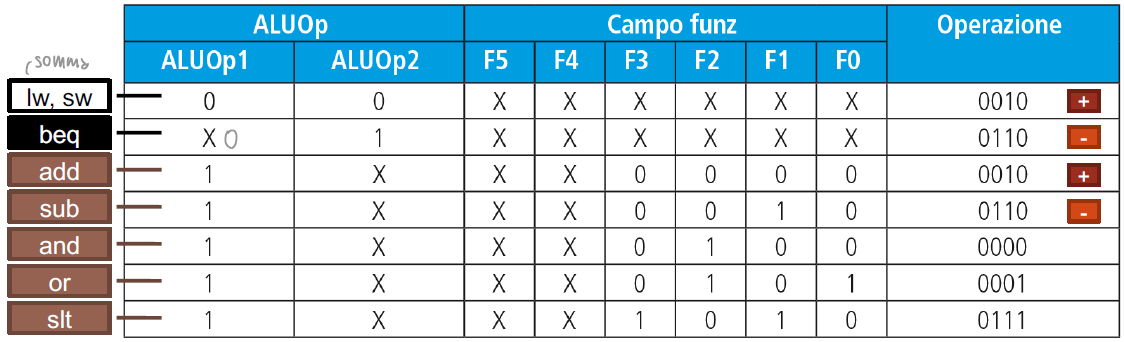

la control unit genera un segnale di controllo a 6 bit - opcode e funct, che definisce che tipo di operazione verrà svolta dalla ALU

| ALU control line | funzione | |

|---|---|---|

0000 | AND | |

0001 | OR | |

0010 | add | |

0110 | subtract | |

0111 | set on less that | |

1100 | NOR | |

| La logica di controllo della ALU è implementata “a cascata” - in base ai bit della ALUop, ci sono 3 casi: |

- devo guardare funct

- somma

- sottrazione

visto che sono 3 opzioni, si utilizzeranno 2 bit.

Se il MSB della ALUOp è:

- 1 - devo controllare il campo funct

- 0:

- se il secondo bit è 0 - faccio una somma

- se il secondo bit è 1 - faccio una sottrazione

il valore dell’ingresso di controllo della ALU viene generato dopo una decodifica basata sulla ALUOp.

| codice istruzione | ALUOp | campo funzione | op. ALU | ingresso controllo ALU |

|---|---|---|---|---|

lw | 00 | XXXXXX | somma | 0010 |

sw | 00 | XXXXXX | somma | 0010 |

beq | 01 | XXXXXX | sottraz. | 0110 |

tipo R | 10 | [10] 0000 | somma | 0010 |

tipo R | 10 | [10] 0010 | sottraz. | 0110 |

tipo R | 10 | [10] 0100 | AND | 0000 |

tipo R | 10 | [10] 0101 | OR | 0001 |

tipo R | 10 | [10] 1010 | slt | 0111 |

input di controllo e tavola di verità

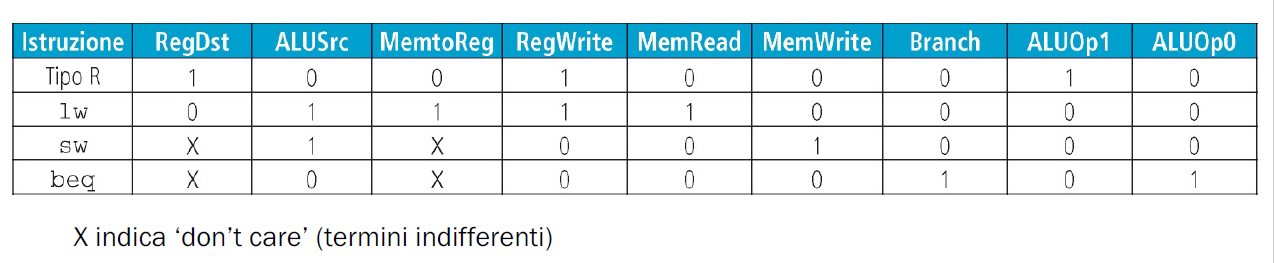

segnali di controllo

| segnale | effetto se asserito | effetto se non asserito |

|---|---|---|

RegDst | il numero del registro di scrittura viene dal campo rd (but 15-11) | il numero del registro di scrittura viene dal campo rt (bit 20-16) |

RegWrite | il dato viene scritto nel register file nel registro con il numero “registro di scrittura” | nulla |

ALUsrc | il secondo operando della ALU viene dall’estensione del segno dei 16 bit meno significativi (tipo immediate?) | il secondo operando della ALU viene dalla seconda uscita del register file (dato letto 2) |

MemRead | il dato della memoria nella posizione indicata viene mandato in uscita sulla linea “dato letto” | nulla |

MemWrite | il contenuto della memoria nella posizione puntata dall’indirizzo viene sostituito con il contenuto della linea “dato scritto” | nulla |

MemtoReg | il dato inviato al register file per la scrittura viene dalla Memoria Dati | il dato inviato al register file per la scrittura viene dalla ALU |

segnali Control Unit

i segnali che la CU produrrà per i diversi tipi di istruzione saranno:

tempi di esecuzione

se conosciamo il tempo necessario a produrre i risultati delle diverse unità funzionali, siamo in grado di calcolare il tempo totale di ciascuna istruzione